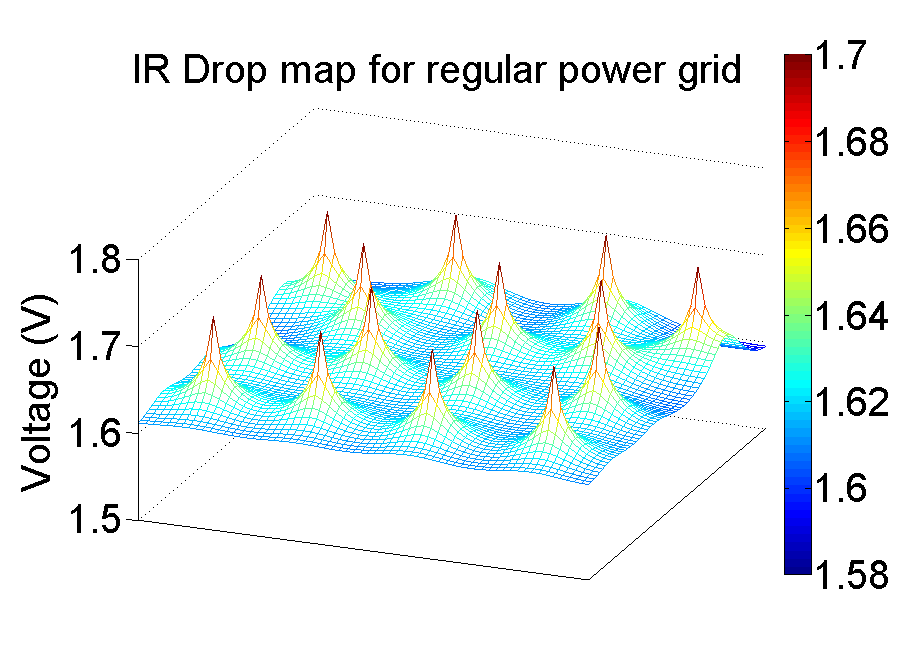

Robust power delivery is an increasingly important design task in modern integrated circuits (ICs) due to increasing power and power density. This power increase complicates power supply network (PSN) design and the ability to satisfy the static IR voltage drop, transient voltage droop and electromigration current constraints. The large amount of power used by modern ICs also leads to high on chip temperature which exacerbates the PSN design problems. My research focuses on robust PSN design, in the presence of reliability problems caused by high chip temperatures. The first project focused on redundant power pin, to ensure a PSN can meet all voltage and electromigration constraints in the presence of single-pin failure. The second project focused on decap placement to reduce joule heating and subsequently interconnect temperatures in PSNs.

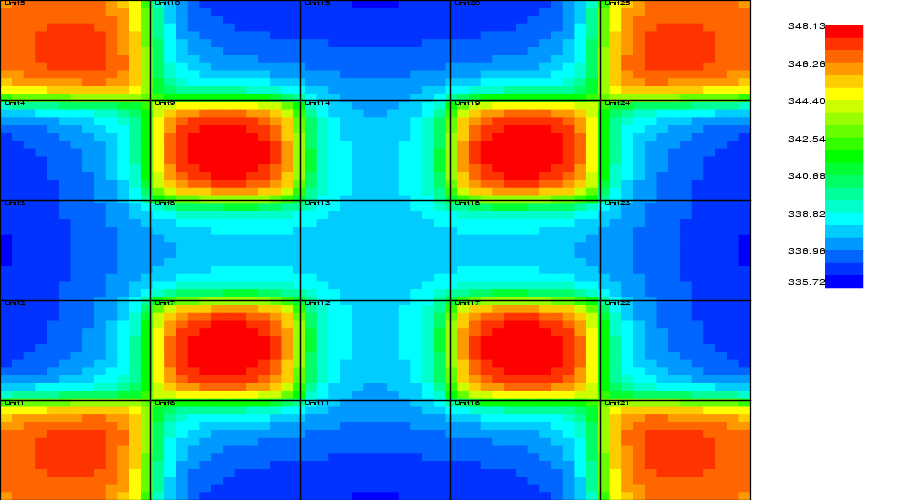

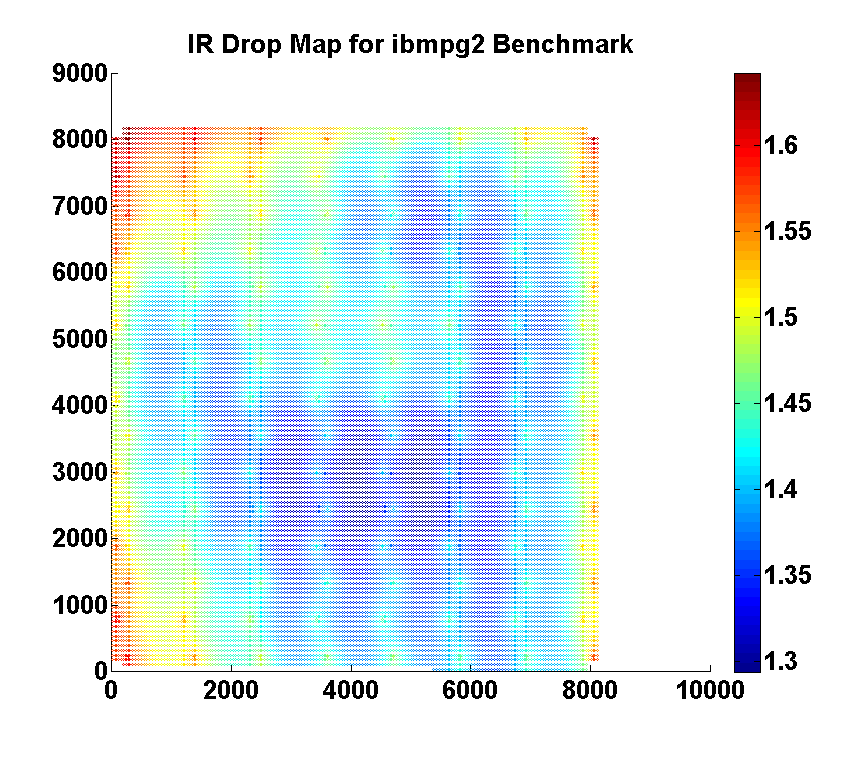

Image of static IR Drop for the IBM ibmpg2 power grid benchmark

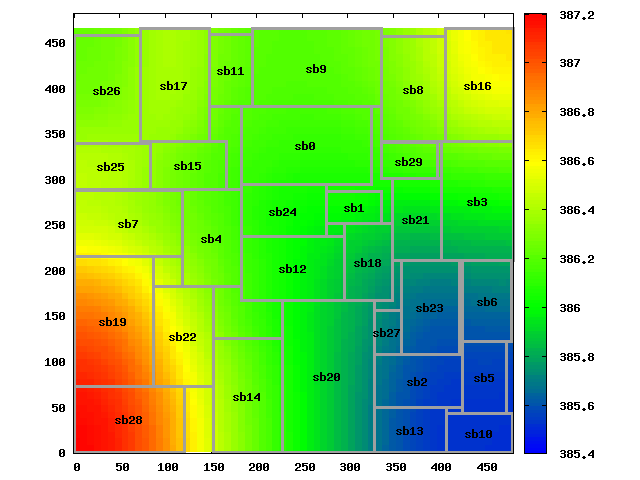

Transient simulation video for the IBM ibmpg2t transient power grid benchmark